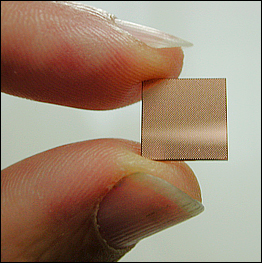

인텔 코리아(사장 김명찬 www.intel.com/kr)는 인텔이 세계에서 가장 앞선 65나노미터 공정 기술을 이용해 70메가비트 SRAM(Static Random Access Memory)칩을 개발했다고 31일 발표했다.

인텔은 "65나노미터 공정을 이용해 5억개의 트랜지스터를 집적했고, 이 트랜지스터내에서 스위치 역할을 하는 게이트 크기는 이전 90나노미터 공정기술로 만들어진 게이트에 비해 30%가량 크기가 줄어들었다"고 말했다.

회사는 지난 해 11월, 4메가비트 SRAM 개발에 65나노미터 공정 기술을 적용한다고 발표한 이래 이번에 70메가비트 SRAM 제작에 성공했다. 70메가비트 SRAM을 장착한 제품은 오는 2005년 초부터 생산될 예정이다.

선린 차우(Sunlin Chou) 인텔 수석 부사장 겸 기술 및 생산 그룹 총괄은 "최고의 집적도와 절전 기능을 보유한 65나노미터 공정 기술 도입으로 더욱 향상된 성능의 칩을 생산할 수 있게 됐다"고 자랑했다.

슬립 트랜지스터는 SRAM이 작동하지 않을 때는 통하는 전류를 차단시켜 칩상에서의 전력 소모를 대폭 감소시킬 수 있다.

인텔의 65나노미터 제조공정에 대한 자세한 내용은 오는 12월 12일부터 15일까지 샌프란시스코에서 열리는 국제전기전자학회 (IEEE) 주최 국제전자장비회의에서 발표될 예정이다.

--comment--

첫 번째 댓글을 작성해 보세요.

댓글 바로가기